Abbas Rahimi · Luca Benini Rajesh K. Gupta

From Variability

Tolerance to Approximate

Computing in Parallel

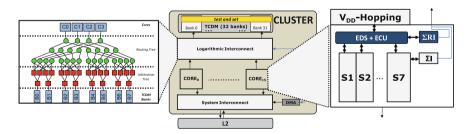

Integrated Architectures

and Accelerators

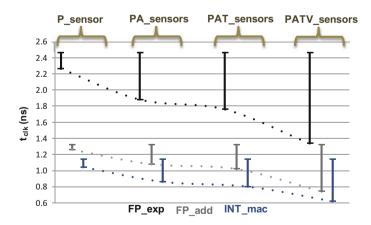

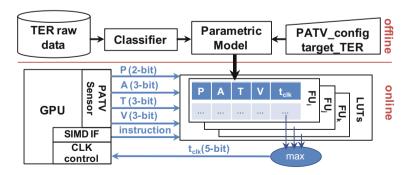

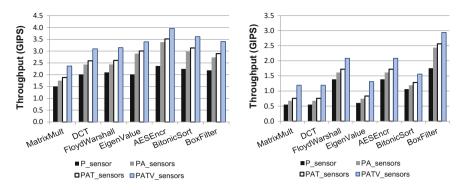

From Variability Tolerance to Approximate Computing in Parallel Integrated Architectures and Accelerators

Abbas Rahimi · Luca Benini Rajesh K. Gupta

From Variability Tolerance to Approximate Computing in Parallel Integrated Architectures and Accelerators

Abbas Rahimi

Department of Electrical Engineering

and Computer Sciences

University of California Berkeley

Berkeley, CA

USA

Luca Benini Integrated Systems Laboratory ETH Zurich Zürich Switzerland Rajesh K. Gupta

Department of Computer Science

and Engineering

University of California, San Diego

La Jolla, CA

USA

ISBN 978-3-319-53767-2 DOI 10.1007/978-3-319-53768-9 ISBN 978-3-319-53768-9 (eBook)

Library of Congress Control Number: 2017932004

#### © Springer International Publishing AG 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer International Publishing AG

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

To my wife with everlasting love and gratitude

-Abbas Rahimi

#### **Foreword**

There is no question that computing has dramatically changed society, and has furthered humanity in ways that were hard to foresee at its onset. Many factors have contributed to its unfettered success including the adoption of Boolean logic and algorithmic thinking, the invention of the instruction set machine, and the advent of the semiconductor technology. The latter offered us a semi-perfect switch device and effective ways of storing data. All these factors have led to an amazing run of almost 7 decades. Over time, the quest for ever higher performance in the presence of power and energy limitations have forced us to make major changes to how the processors were architected and operated—such as the introduction of concurrency, the adoption of co-processors and accelerators, or the adoption of ever more complex memory hierarchies. However, in essence the fundamentals remained unchanged

For a number of reasons, this model is at the verge of undergoing some major changes and challenges. On the one hand, the scaling model of semiconductors—commonly known as Moore's law—is running out of steam, hence depriving us from a convenient means in improving computational performance, density and efficiency. On the other hand, the nature of computation itself is changing with data rather than algorithm taking primacy. Both these trends force us to reflect on some of the foundational concepts that have driven computation for such a long period. In an abundance of data, statistical distributions become more relevant than deterministic answers. Many perceptual tasks related to human-world interaction fall under the same class. Learning-based programming approaches are gaining rapid interest and influence. Simultaneously the lack of "the perfect switch", as well as the high-variability of nanoscale devices operating under high energy-efficiency (that is, low-voltage) makes deterministic computing an extremely expensive if at all possible undertaking.

All of this has made researchers explore novel computational models that are "approximate" in nature. This means that errors and approximations are becoming acceptable as long as the outcomes have a well-defined statistical behavior. A number of approaches have been identified and are being actively pursued under

viii Foreword

different headers such as approximate computing, statistical computing and stochastic processing. In this book, the authors investigate how errors caused by variation (especially those caused by timing) can be exposed to the software layers, and how they can be mitigated using a range of techniques and methods to reduce their impact. The document provides a clear insight of what is possible through pure software intervention.

This book is at the forefront of what is to come at the frontiers in the new age of computation. As such, I heartily recommend it as a great intellectual effort and a superb read.

Jan M. Rabaey

#### **Preface**

Variation in performance and power across manufactured parts and their operating conditions is an accepted reality in modern microelectronic manufacturing processes with geometries in nanometer scales. This book views such variations both as a challenge as well an opportunity to rearchitect the hardware/software interface that provides more resilient system architectures. We start with an examination of how variability manifests itself across various levels of microelectronic systems. We examine various mechanisms designers use, and can use, to combat negative effects of variability.

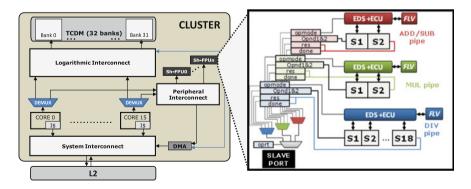

This book attempts a comprehensive look at the entire software/hardware stack and system architecture in order to devise effective strategies to address microelectronic variability. First, we review the key concepts on timing errors caused by various variability sources. We use a two-pronged strategy to mitigate such errors by jointly exposing hardware variations to the software and by exploiting flexibility made possible by parallel processing. We consider methods to predict and prevent, detect and correct, and finally conditions under which such errors can be accepted. For each of these methods, our work spans defining and measuring the notion of error tolerance at various levels, from instructions to procedures to parallel programs. These measures essentially capture the likelihood of errors and associated cost of error correction at different levels. The result is a design platform that enables us to combine these methods that enable detection and correction of erroneous results within a defined criterion for acceptable errors using a notion of memoization across the hardware/software interface. Pursuing this strategy, we develop a set of software techniques and microarchitecture optimizations for improving cost and scale of these methods in massively parallel computing units, such as general-purpose graphics processing units (GP-GPUs), clustered many-core architectures, and field-programmable gate array (FPGA) accelerators.

Our results show that parallel architectures and use of parallelism in general provides the best means to combat and exploit variability. Using such programmable parallel accelerator architectures, we show how system designers can

x Preface

coordinate propagation of error information and its effects along with new techniques for memoization and memristive associative memory. This book naturally leads to use of these techniques into emerging area of approximate computing, and how these can be used in building resilient and efficient computing systems.

Berkeley, USA Zürich, Switzerland San Diego, USA January 2017 Abbas Rahimi Luca Benini Rajesh K. Gupta

### **Contents**

| 1   | Intro  | duction                                                   | 1  |

|-----|--------|-----------------------------------------------------------|----|

|     | 1.1    | Sources of Variability                                    | 1  |

|     | 1.2    | Delay Variation                                           | 2  |

|     | 1.3    | Book Organization                                         | 4  |

|     | Refer  | ences                                                     | 6  |

| Par | t I P  | redicting and Preventing Errors                           |    |

| 2   | Instru | uction-Level Tolerance                                    | 11 |

|     | 2.1    | Introduction                                              | 11 |

|     | 2.2    | Effect of Operating Conditions                            | 12 |

|     | 2.3    | Delay Variation Among Pipeline Stages                     | 13 |

|     | 2.4    | Instruction Characterization Methodology and Experimental |    |

|     |        |                                                           | 15 |

|     |        | 2.4.1 Gate-Level Simulation                               | 15 |

|     |        | 2.4.2 Instruction-Level Delay Variability                 | 16 |

|     |        |                                                           | 17 |

|     |        |                                                           | 18 |

|     | 2.5    | Chapter Summary                                           | 19 |

|     | Refer  | ± · · · · · · · · · · · · · · · · · · ·                   | 19 |

| 3   | Seque  | ence-Level Tolerance                                      | 21 |

|     | 3.1    | Introduction                                              | 21 |

|     | 3.2    | PVT Variations                                            | 22 |

|     |        | 3.2.1 Conventional Static Timing Analysis                 | 24 |

|     |        | · · · · · · · · · · · · · · · · · · ·                     | 26 |

|     | 3.3    | Error-Tolerant Applications                               | 27 |

|     |        | 3.3.1 Analysis of Adaptive Guardbanding                   |    |

|     |        | · · · · · · · · · · · · · · · · · · ·                     | 28 |

xii Contents

|   | 3.4  | Error-Intolerant Applications                           | 30  |

|---|------|---------------------------------------------------------|-----|

|   |      | 3.4.1 Sequence-Level Vulnerability (SLV)                | 30  |

|   |      | 3.4.2 SLV Characterization                              | 31  |

|   | 3.5  | Adaptive Guardbanding                                   | 35  |

|   | 3.6  | Experimental Results                                    | 37  |

|   |      | 3.6.1 Effectiveness of Adaptive Guardbanding            | 39  |

|   |      | 3.6.2 Overhead of Adaptive Guardbanding                 | 44  |

|   | 3.7  | Chapter Summary                                         | 44  |

|   | Refe | rences.                                                 | 45  |

| 4 | Proc | edure-Level Tolerance                                   | 47  |

|   | 4.1  | Introduction                                            | 47  |

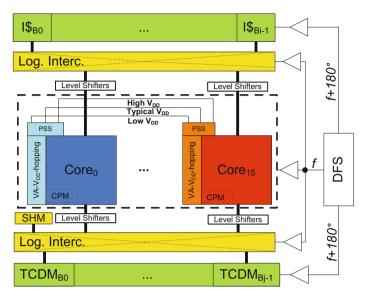

|   | 4.2  | Variation-Tolerant Processor Clusters Architecture      | 48  |

|   |      | 4.2.1 Variation-Aware VDD-Hopping                       | 49  |

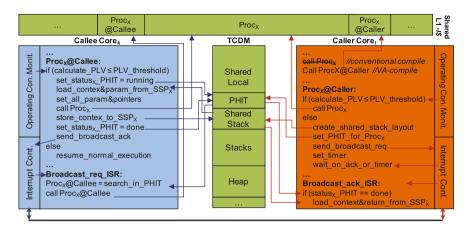

|   | 4.3  | Procedure Hopping for Dynamic IR-Drop                   | 51  |

|   |      | 4.3.1 Supporting Intra-cluster Procedure Hopping        | 51  |

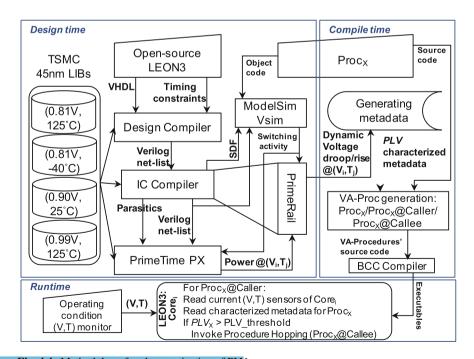

|   | 4.4  | Characterization of PLV to Dynamic Operating Conditions | 54  |

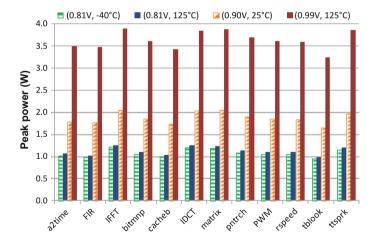

|   | 4.5  | Experimental Results                                    | 55  |

|   | 1.0  | 4.5.1 Cost of Procedure Hopping                         | 57  |

|   | 4.6  | Chapter Summary                                         | 59  |

|   |      | rences.                                                 | 59  |

|   |      |                                                         | - / |

| 5 |      | nel-Level Tolerance                                     | 61  |

|   | 5.1  | Introduction                                            | 61  |

|   | 5.2  | Device-Level NBTI Model                                 | 62  |

|   | 5.3  | GP-GPU Architecture                                     | 64  |

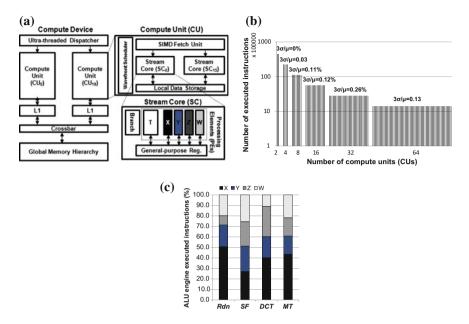

|   |      | 5.3.1 GP-GPU Workload Distribution                      | 64  |

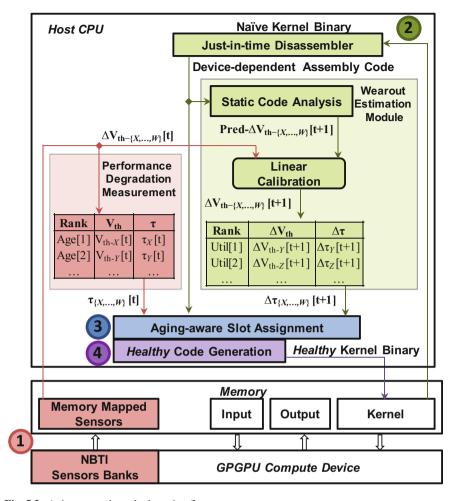

|   | 5.4  | Aging-Aware Compilation                                 | 66  |

|   |      | 5.4.1 Observability: Aging Sensors                      | 67  |

|   |      | 5.4.2 Prediction: Wearout Estimation Module             | 68  |

|   |      | 5.4.3 Controllability: Uniform Slot Assignment          | 68  |

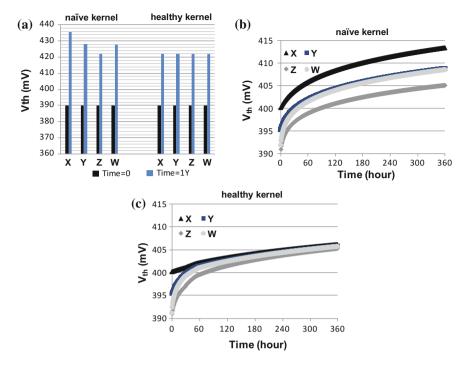

|   | 5.5  | Experimental Results                                    | 70  |

|   | 5.6  | Chapter Summary                                         | 73  |

|   | Refe | rences                                                  | 73  |

| 6 | Hier | archically Focused Guardbanding                         | 75  |

|   | 6.1  | Introduction                                            | 75  |

|   | 6.2  | Timing Error Model for PVTA                             | 76  |

|   | 0.2  | 6.2.1 Analysis Flow for Timing Error Extraction         | 76  |

|   |      | 6.2.2 Parametric Model Fitting                          | 78  |

|   |      | 6.2.3 TER Classification.                               | 80  |

|   |      | 6.2.4 Robustness of Classification                      | 81  |

|   | 6.3  | Runtime Hierarchically Focused Guardbanding             | 81  |

|   | 0.5  | 6.3.1 Observability                                     | 83  |

|   |      | 6.3.2 Controllability                                   | 84  |

|   |      | o.c condomicing                                         | O F |

Contents xiii

|      | 6.4<br>6.5<br>Refe | A Case Study of HFG on GPUs.  Chapter Summary        | 85<br>86<br>87 |  |  |  |  |  |  |  |  |  |  |

|------|--------------------|------------------------------------------------------|----------------|--|--|--|--|--|--|--|--|--|--|

| Part | II                 | <b>Detecting and Correcting Errors</b>               |                |  |  |  |  |  |  |  |  |  |  |

| 7    | Wor                | ·k-Unit Tolerance                                    | 91             |  |  |  |  |  |  |  |  |  |  |

|      | 7.1                | Introduction                                         | 91             |  |  |  |  |  |  |  |  |  |  |

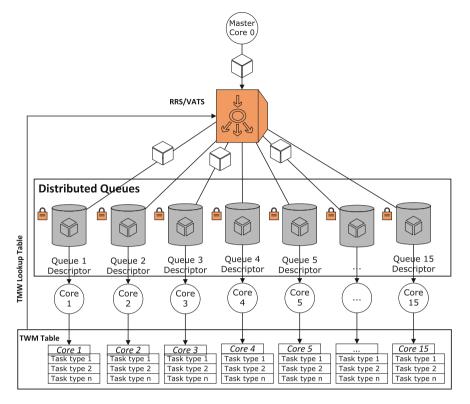

|      | 7.2                | Architectural Support for VOMP                       | 94             |  |  |  |  |  |  |  |  |  |  |

|      | 7.3                | Work-Unit Vulnerability and VOMP Work-Sharing        | 95             |  |  |  |  |  |  |  |  |  |  |

|      |                    | 7.3.1 Intra- and Inter-corner WUV                    | 98             |  |  |  |  |  |  |  |  |  |  |

|      |                    | 7.3.2 Online WUV Characterization                    | 103            |  |  |  |  |  |  |  |  |  |  |

|      | 7.4                | VOMP Schedulers                                      | 105            |  |  |  |  |  |  |  |  |  |  |

|      |                    | 7.4.1 Variation-Aware Task Scheduling (VATS)         | 105            |  |  |  |  |  |  |  |  |  |  |

|      |                    | 7.4.2 Variation-Aware Section Scheduling (VASS)      | 108            |  |  |  |  |  |  |  |  |  |  |

|      | 7.5                | Experimental Results                                 | 109            |  |  |  |  |  |  |  |  |  |  |

|      |                    | 7.5.1 Framework Setup                                | 109            |  |  |  |  |  |  |  |  |  |  |

|      |                    | 7.5.2 VOMP Results for Tasking                       | 110            |  |  |  |  |  |  |  |  |  |  |

|      |                    | 7.5.3 VOMP Results for Sections                      | 112            |  |  |  |  |  |  |  |  |  |  |

|      | 7.6                | Chapter Summary                                      | 113            |  |  |  |  |  |  |  |  |  |  |

|      | Refe               | erences                                              | 114            |  |  |  |  |  |  |  |  |  |  |

| 8    | Men                | nristive-Based Associative Memory for Error Recovery | 117            |  |  |  |  |  |  |  |  |  |  |

| U    | 8.1                | Introduction                                         | 117            |  |  |  |  |  |  |  |  |  |  |

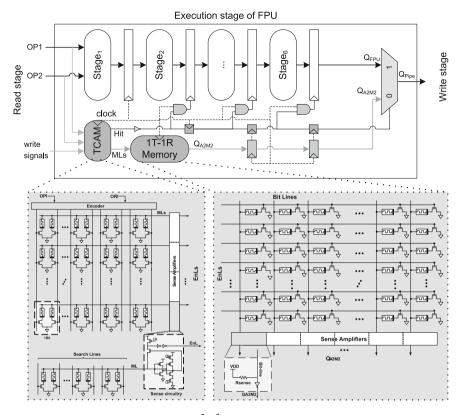

|      | 8.2                | Energy-Efficient GP-GPUs                             | 119            |  |  |  |  |  |  |  |  |  |  |

|      | 0.2                | 8.2.1 Associative Memristive-Based Computing         | 120            |  |  |  |  |  |  |  |  |  |  |

|      | 8.3                | Collaborative Compilation                            | 122            |  |  |  |  |  |  |  |  |  |  |

|      | 0.5                | 8.3.1 FPU Memristive-Based Computing                 | 124            |  |  |  |  |  |  |  |  |  |  |

|      | 8.4                | Experimental Results                                 | 125            |  |  |  |  |  |  |  |  |  |  |

|      | 0.4                | 8.4.1 FPUs with AMM Modules                          | 125            |  |  |  |  |  |  |  |  |  |  |

|      |                    |                                                      | 126            |  |  |  |  |  |  |  |  |  |  |

|      | 0 5                |                                                      | 129            |  |  |  |  |  |  |  |  |  |  |

|      | 8.5                | Chapter Summary                                      | 129            |  |  |  |  |  |  |  |  |  |  |

|      | References         |                                                      |                |  |  |  |  |  |  |  |  |  |  |

| Part | III                | Accepting Errors                                     |                |  |  |  |  |  |  |  |  |  |  |

| 9    | Accı               | uracy-Configurable OpenMP                            | 133            |  |  |  |  |  |  |  |  |  |  |

|      | 9.1                | Introduction                                         | 133            |  |  |  |  |  |  |  |  |  |  |

|      | 9.2                | Controlled Approximation                             | 135            |  |  |  |  |  |  |  |  |  |  |

|      | 9.3                | Accuracy-Configurable OpenMP Environment             | 136            |  |  |  |  |  |  |  |  |  |  |

|      | 7.0                | 9.3.1 Accuracy-Configurable FPUs                     | 136            |  |  |  |  |  |  |  |  |  |  |

|      |                    | 9.3.2 OpenMP Compiler Extension for Approximation    | 137            |  |  |  |  |  |  |  |  |  |  |

|      |                    | 9.3.3 Runtime Support                                | 138            |  |  |  |  |  |  |  |  |  |  |

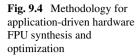

|      |                    | 9.3.4 Application-Driven Hardware FPU Synthesis      | 130            |  |  |  |  |  |  |  |  |  |  |

|      |                    | and Ontimization                                     | 130            |  |  |  |  |  |  |  |  |  |  |

xiv Contents

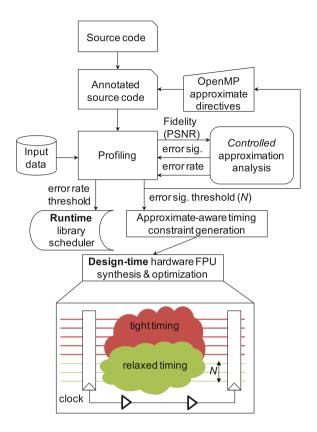

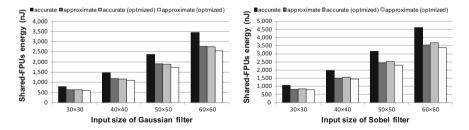

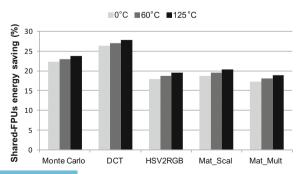

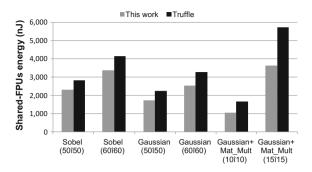

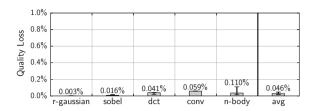

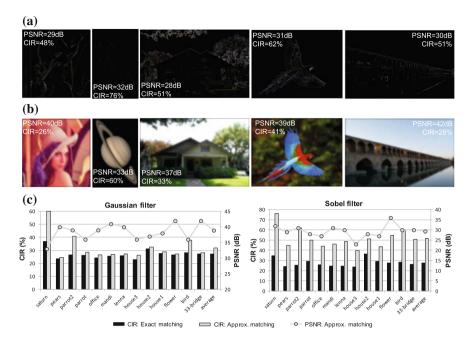

|    | 9.4   | Experimental Results                                        | 141 |

|----|-------|-------------------------------------------------------------|-----|

|    |       | 9.4.1 Error-Tolerant Applications                           | 142 |

|    |       | 9.4.2 Error-Intolerant Applications                         | 146 |

|    | 9.5   | Chapter Summary                                             | 147 |

|    | Refer | ences                                                       | 148 |

| 10 |       | pproximation Workflow for Exploiting Data-Level             |     |

|    | Paral | lelism in FPGA Acceleration                                 | 151 |

|    | 10.1  | Introduction                                                | 151 |

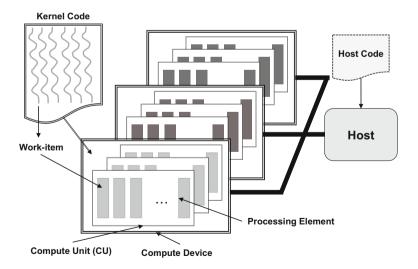

|    | 10.2  | OpenCL Execution Model                                      | 153 |

|    |       | 10.2.1 Mapping OpenCL Programs on FPGAs                     | 153 |

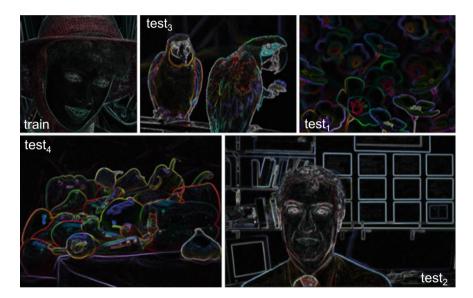

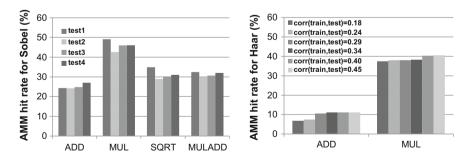

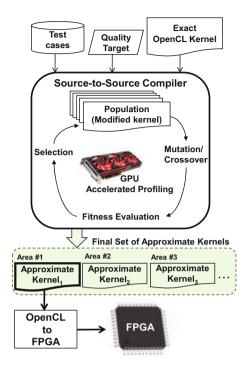

|    | 10.3  | Grater: Approximation Design Workflow                       | 154 |

|    |       | 10.3.1 Analysis and Pruning                                 | 155 |

|    |       | 10.3.2 Genetic-Based Approximation Algorithm                | 156 |

|    | 10.4  | Experimental Results                                        | 159 |

|    |       | 10.4.1 Experimental Setup                                   | 159 |

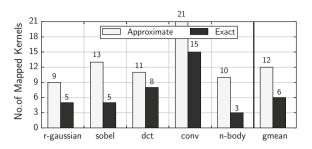

|    |       | 10.4.2 Area Savings with Approximate Kernels                | 160 |

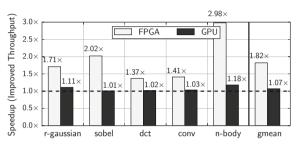

|    |       | 10.4.3 Speedup                                              | 160 |

|    | 10.5  | Chapter Summary                                             | 163 |

|    | Refer | ences                                                       | 163 |

| 11 | Mem   | ristive-Based Associative Memory for Approximate            |     |

|    | Comp  | putational Reuse                                            | 165 |

|    | 11.1  | Introduction                                                | 165 |

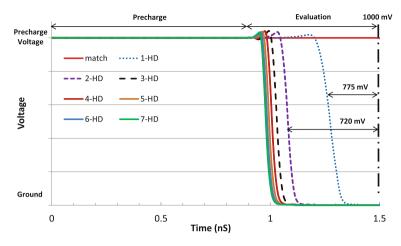

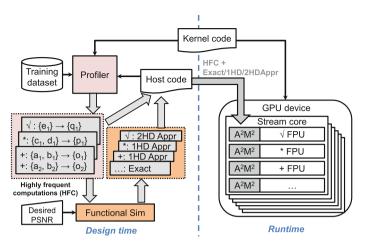

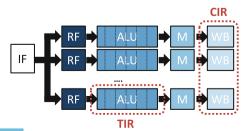

|    | 11.2  | GPU Architecture Using A <sup>2</sup> M <sup>2</sup> Module | 167 |

|    |       | 11.2.1 Southern Islands Architecture                        | 167 |

|    |       | 11.2.2 Approximate Associative Memristive Memory            |     |

|    |       | Module                                                      | 168 |

|    | 11.3  | Framework to Support A <sup>2</sup> M <sup>2</sup>          | 171 |

|    |       | 11.3.1 Execution Flow                                       | 171 |

|    |       | 11.3.2 Design Space for A <sup>2</sup> M <sup>2</sup>       | 173 |

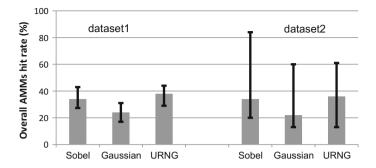

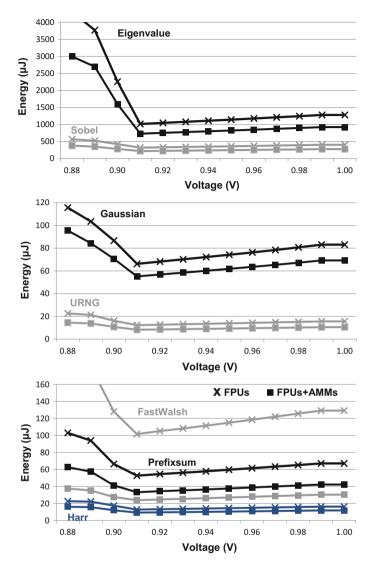

|    | 11.4  | Experimental Results                                        | 175 |

|    |       | 11.4.1 Experimental Setup                                   | 175 |

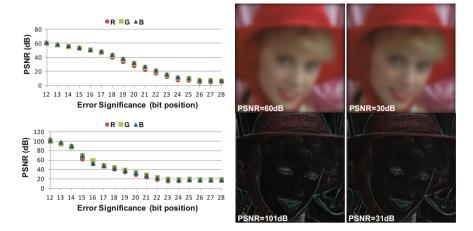

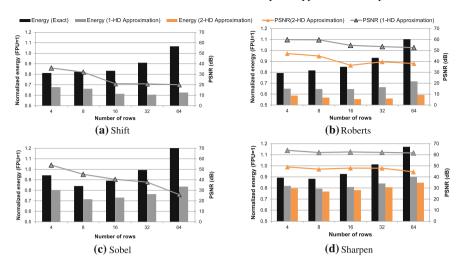

|    |       | 11.4.2 Energy Saving with Corresponding PSNR                | 177 |

|    | 11.5  | Chapter Summary                                             | 178 |

|    | Refer | ences                                                       | 179 |

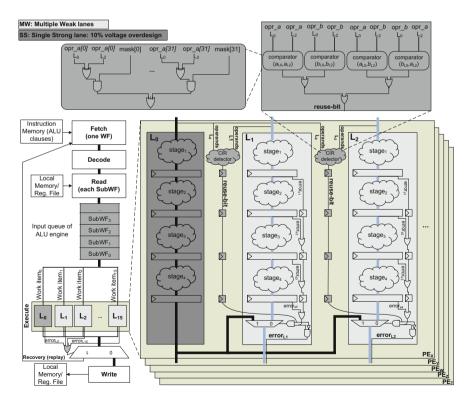

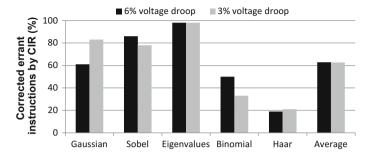

| 12 | Spati | al and Temporal Memoization                                 | 181 |

|    | 12.1  | Introduction                                                | 182 |

|    | 12.2  | Spatial Memoization (Concurrent Instruction Reuse)          | 183 |

|    |       | 12.2.1 Single Strong Multiple Weak (SSMW)                   |     |

|    |       | Architecture                                                | 184 |

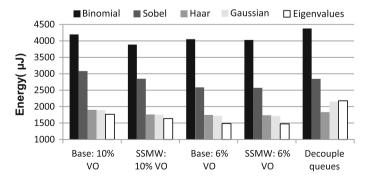

|    |       | 12.2.2 Experimental Results                                 | 186 |

|    | 12.3  | Temporal Memoization (Temporal Instruction Reuse)           | 188 |

Contents xv

|     |       | 12.3.1 Temporal Memoization for Error Recovery 18 | 88 |

|-----|-------|---------------------------------------------------|----|

|     |       | 12.3.2 Experimental Results                       | 89 |

|     | 12.4  | Chapter Summary                                   | 89 |

|     |       | rences                                            |    |

| 13  | Outlo | ook                                               | 91 |

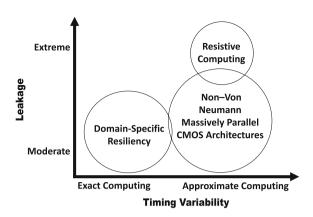

|     | 13.1  | Domain-Specific Resiliency                        | 91 |

|     |       | 13.1.1 Software                                   | 91 |

|     |       | 13.1.2 Architecture                               | 92 |

|     |       | 13.1.3 Circuit                                    | 92 |

|     | 13.2  | Non-Von Neumann Massively Parallel Architectures  | 93 |

| Ind | ev    | 10                                                | 95 |

### Chapter 1 Introduction

Chapter Summary Variation in performance and power consumption is a common phenomenon in semiconductor manufacturing. What makes it particularly challenging, however, is its effect on manufacturing of devices as these scale down to near atomic scale feature dimensions. Any variation in dimensions, doping, etc, has a large effect on the resulting device and circuit behavior. To address this variation, designers resort to design **guardbands**. These guardbands are increasing rapidly and eventually obliterating any gains due to device scaling. As a consequence, reduction of design guardbands in design has become an important research challenge with recent results that recover a part of these guardbands through circuit-level changes. We begin by examining sources of variability in integrated circuits and conclude with an outline of the entire book.

#### 1.1 Sources of Variability

Broadly speaking, there are three physical types of variations: (i) Spatial variability: Process variations cause static variations in critical dimension, channel length (L), and threshold voltage  $(V_{th})$  of devices due to dopant fluctuations and sub-wavelength lithography. These variations manifest themselves as die-to-die (D2D) and withindie (WID) variations [1]. D2D variations affect all devices on a die equally, whereas WID variations induce different characteristics for each device. (ii) Temporal variability: Aging and wearout mechanisms cause slow temporal degradation in devices reliability. Device aging mechanisms are induced by negative bias temperature instability (NBTI), positive bias temperature instability, electromigration, time-dependent dielectric breakdown, gate oxide integrity, thermal cycling, and hot carrier injection [2]. (iii) Dynamic variability: Environmental variations in ambient condition are caused by fluctuations in operating temperature and supply voltage droops. Voltage droops result from abrupt changes in the switching activity, inducing large current transients in the power delivery system (dI/dt voltage drops), and contain highfrequency and low-frequency components which occur locally as well as globally across the die [3]. On the other hand, temperature variations occur at a relatively slow time scale with local hot spots on the die, depending on environmental, and workload

1

2 1 Introduction

conditions [4]. The origins of variability include time-independent DC component (process variations), slow-varying low-frequency components (aging and temperature), and fast-changing high-frequency components (voltage droops). The variations are expected to be worse with technology scaling [5].

Spatial parameter variations in the device geometries in conjunction with temporal degradation and undesirable fluctuations in the operating condition may prevent circuit from meeting the performance and power constraints. The most immediate manifestations of variability are in path delay (therefore, performance) and power variations. Sequential elements are connected at the end of the paths to hold the circuit state. Path delay variations cause violation of timing specification resulting in circuitlevel timing errors that could lead to an invalid state being stored in the sequential element. This could result in a malfunction of the digital system. Synchronous circuit designers commonly handle the timing errors by adding safety timing margins to the voltage and/or the clock frequency as guardband. This practice leads to overly conservative designs. Currently, the guardbands tend to accumulate as design closure is performed using a multi-corner analysis, with an increasing number of corners [1, 6, 7]. As a result, the impact of guardbanding on the key design metrics (power, performance, and area) has been steadily increasing with technology scaling [5], leading to loss of operational efficiency and increased costs due to overdesign. Power variability is also challenging, for instance 13× variation in the sleep power across ten instances of ARM Cortex M3 core was observed over a temperature range of 22-60 °C [8]. This thesis focuses instead on the path delay variation and its manifestation as timing errors. We identify the timing error as the most threatening manifestation of variability and investigate various means to address it. We begin with a quantitative feel of the extent of variation currently seen in manufactured devices. Section 1.2 covers the delay variation in details.

#### 1.2 Delay Variation

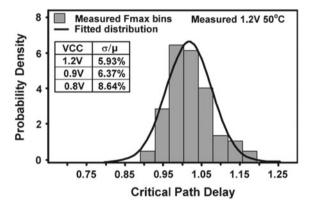

For an Intel 80-core processor in 65 nm, Fig. 1.1 shows the WID core-to-core maximum frequency (Fmax) variations for each of the 80 cores. The measurements have been done at a fixed operating temperature of  $50\,^{\circ}\text{C}$  with three operating voltages: 1.2, 0.9, and 0.8 V. At the nominal voltage of 1.2 V, the fastest core displays the Fmax of 7.3 GHz while in the same die the slowest core can work with the Fmax of 5.7 GHz resulting in 28% WID clock frequency variation. Figure 1.2 illustrates the delay distribution of the 80 cores for the same operating conditions [9]. The single die with 80 cores exhibits an increasing value of  $\sigma/\mu$  for lower voltages: 5.93, 6.37, and 8.64% for 1.2, 0.9, and 0.8 V, respectively. Lowering the voltage from the nominal 1.2 to 0.8 V, increases the critical paths variability  $(\sigma/\mu)$  by 45% [9].

Voltage overscaling (VOS) [10] and working at near-threshold (NT) voltage [11] have become popular approaches for building energy-efficient digital circuits. Operating at low voltages ( $V_{DD} \leq 0.5 \, \text{V}$ ) unfortunately exacerbates the effects of delay variations [10, 12–15]. This indicates the importance of variability awareness at

1.2 Delay Variation 3

Fig. 1.1 WID core-to-core maximum clock frequency variation for 80 cores on a single chip [9]

Measured 50°C — 1.2V — 0.9V — 0.8V

7

7.3 GHz

6

7

7

10

20

30

40

50

60

70

80

Core ID

Fig. 1.2 Critical path delay distribution and its coefficient of variation  $(\sigma/\mu)$  for 80 cores on a single chip [9]

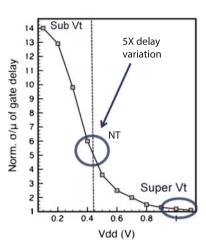

lower operating voltages, where the delay uncertainty is further increased. The WID delay measurement for a 45 nm SIMD processor shows that reducing  $V_{DD}$  from 1.0 to 0.53 V increases the delay variation by  $6 \times [15]$ . Figure 1.3 shows the normalized gate delay variation due to process variations as a function of  $V_{DD}$  [12]. Working at near-threshold voltage of 400 mV increases the performance variability by  $5 \times$  compared to  $1.3 \times$  at the nominal operating voltage. It is then clear that for logic working at near-threshold voltages, the statistical WID variation in the voltage threshold  $(V_{th})$  plays an important role in determining the path delay.  $V_{th}$  variations result mainly from random fluctuations in the number of dopant atoms in the transistor channels [13]. Considering dynamic sources of variations, including temperature fluctuations, and voltage droops results in a total performance variability of  $20 \times [12]$ .

Given such a growing increase in performance variability, design methods are needed to make a design resilient to timing errors, especially for circuits operating at low voltages where the effect of delay uncertainty is pronounced. The effects of the static process variations can sometimes be mitigated through binning or by post-silicon tuning during test time, while the dynamic variations manifest themselves on the field as a function of time and environment, and therefore cannot be compensated by *one-time* pre-silicon and post-silicon tuning techniques. Consequently, accurate design time analysis coupled with efficient runtime techniques are required to overcome the variability challenges.

المنسلون للاستشارات

4 1 Introduction

Fig. 1.3 Impact of voltage scaling on gate delay variation due to process variation [12]

#### 1.3 Book Organization

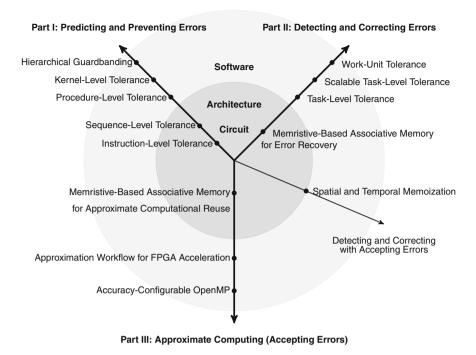

This book grew out of a doctoral dissertation at the University of California, San Diego [16]. This book focuses on timing errors caused by various sources of variations at different levels. We devise methods to mitigate such errors by jointly **exposing hardware variations to the software** and by **exploiting parallel processing**. We investigate methods to *predict and prevent*, *detect and correct*, and finally conditions under which errors can be *accepted*. We classify our proposed methods into a conceptual Y-chart shown in Fig. 1.4.

The Y-chart in Fig. 1.4 groups these methods to address variability into three parts based on *when* and *how* the timing errors should be manipulated. These three parts of the Y-chart are on radial axes. The first axis describes mainly *design time* approaches for predicting and preventing timing errors. The second axis focuses on *runtime* approaches for detecting and correcting timing errors, while the third axis accepts timing errors if possible. Further, we combine these two axes to devise a new joint method of detecting and correcting with accepting errors. Each part is divided into levels of abstraction, using concentric rings. Every abstraction level determines at *which* level of the computing stack the approaches can be applied: *circuit*, *architecture*, and *software*. At the top-level outer ring, we consider approaches applicable to software level; at the lower levels inner rings, we refine approaches into finer architecture, and circuit implementations.

Thus, Fig. 1.4 puts our work in perspective, with the three main axes defining the three separate methodological approaches. For each of these approaches, our work spanned defining and measuring the notion of error tolerance, from instruction set architecture (ISA) to procedures to parallel programs. These measures essentially capture the likelihood of errors and associated cost of error correction at different levels.

Fig. 1.4 Taxonomy of timing error tolerance in this book: abstractions versus approaches

Next natural step is to see the possibility and consequences of relaxing the notion of accuracy and precision in computation. We focus on parallel programming, runtime environment, parallel integrated architecture, and accelerators to support controlled "approximate computing." That is, ensuring safety of error mitigation methods through a set of rules verified by a combination of design-time and runtime constraints. The goal is to deliver functionality within specified quality guarantees. The result is a new joint method of detecting and correcting with accepting errors across the hardware/software interface using memoization techniques spatially or across time (i.e., spatial or temporal reuse of computation). We accordingly devise an arsenal of software techniques and microarchitecture optimizations for improving cost and scale of these methods in massively parallel computing units, such as general-purpose graphics processing units (GP-GPUs), clustered many-core architectures, and field-programmable gate array (FPGA) accelerators. The main focus of our attention for the data-level parallelism is on single instruction, multiple data (SIMD) and GP-GPU architectures, and for the task-level parallelism is on the sharedmemory processor clusters. We find that parallel architectures and parallelism in general provide the best means to combat and exploit variability to design resilient and efficient systems. Using such programmable parallel accelerator architectures, we show how system designers can coordinate propagation of error information and its effects along with new techniques for memoization and memristive associative

6 1 Introduction

memory. This discussion naturally leads to use of these techniques into emerging area of approximate computing, and how these can be used in building resilient and efficient computing systems.

#### References

- K.A. Bowman, S.G. Duvall, J.D. Meindl, Impact of die-to-die and within-die parameter fluctuations on the maximum clock frequency distribution, in IEEE International Solid-State Circuits Conference, Digest of Technical Papers. ISSCC 2001, 278–279 (2001)

- 2. X. Li, J. Qin, J.B. Bernstein, Compact modeling of MOSFET wearout mechanisms for circuit-reliability simulation. IEEE Trans. Device Mater. Reliab. 8(1), 98–121 (2008)

- K. Bowman, C. Tokunaga, J. Tschanz, A. Raychowdhury, M. Khellah, B. Geuskens, S.-L. Lu, P. Aseron, T. Karnik, V. De, Dynamic variation monitor for measuring the impact of voltage droops on microprocessor clock frequency. IEEE Custom Integrated Circuits Conference (CICC) 2010, 1–4 (2010)

- S. Murali, A. Mutapcic, D. Atienza, R. Gupta, S. Boyd, L. Benini, G. De Micheli, Temperature control of high-performance multi-core platforms using convex optimization, in *Proceedings* of the Conference on Design, Automation and Test in Europe, DATE '08, ACM, New York, NY, USA (2008), pp. 110–115

- 5. The ITRS website. http://www.itrs.net/Links/2011ITRS/Home2011.htm

- S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi, V. De, Parameter variations and impact on circuits and microarchitecture. Proceedings of Design Automation Conference 2003, 338–342 (2003)

- T. Austin, V. Bertacco, D. Blaauw, T. Mudge, Opportunities and challenges for better than worst-case design, in *Proceedings of the 2005 Asia and South Pacific Design Automation Conference*, ASP-DAC '05, ACM, New York, NY, USA (2005), pp. 2–7

- 8. L. Wanner, R. Balani, S. Zahedi, C. Apte, P. Gupta, M. Srivastava, Variability-aware duty cycle scheduling in long running embedded sensing systems, in Design. Automation Test in Europe Conference Exhibition (DATE) **2011**, 1–6 (2011)

- S. Dighe, S.R. Vangal, P. Aseron, S. Kumar, T. Jacob, K.A. Bowman, J. Howard, J. Tschanz, V. Erraguntla, N. Borkar, V.K. De, S. Borkar, Within-die variation-aware dynamic-voltage-frequency-scaling with optimal core allocation and thread hopping for the 80-core teraflops processor. IEEE J. Solid-State Circuits 46(1), 184–193 (2011)

- D. Jeon, M. Seok, Z. Zhang, D. Blaauw, D. Sylvester, Design methodology for voltageoverscaled ultra-low-power systems. IEEE Trans. Circuits Syst. II Express. Briefs 59(12), 952–956 (2012)

- B. Zhai, R.G. Dreslinski, D. Blaauw, T. Mudge, D. Sylvester, Energy efficient near-threshold chip multi-processing. ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED) 2007, 32–37 (2007)

- R.G. Dreslinski, M. Wieckowski, D. Blaauw, D. Sylvester, T.N. Mudge, Near-threshold computing: reclaiming moore's law through energy efficient integrated circuits. Proc. IEEE 98(2), 253–266 (2010)

- R. Rithe, S. Chou, J. Gu, A. Wang, S. Datla, G. Gammie, D. Buss, A. Chandrakasan, The effect of random dopant fluctuations on logic timing at low voltage. IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 20(5), 911–924

- M.R. Kakoee, I. Loi, L. Benini, Variation-tolerant architecture for ultra low power shared-l1 processor clusters. IEEE Trans. Circuits Syst. II Express. Briefs 59(12), 927–931 (2012)

References 7

R. Pawlowski, E. Krimer, J. Crop, J. Postman, N. Moezzi-Madani, M. Erez, P. Chiang, A 530mV 10-lane SIMD processor with variation resiliency in 45nm SOI. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) 2012, 492–494 (2012)

Abbas Rahimi, "From Variability-Tolerance to Approximate Computing in Parallel Computing Architectures," Ph.D. Dissertation, Department of Computer Science and Engineering, University of California, San Diego, CA, (2015)

# Part I **Predicting and Preventing Errors**

In this part, we explore approaches to reduce the excessive guardband and enable better than worst-case design while avoiding the timing errors [124–128]. These methods typically use characterization metrics and rely upon modeling that derives rules for simultaneous guardband reduction and error prevention. We show how these methods can be implemented at different abstraction levels, from instructions to kernels. We first characterize instructions for the effect of circuit timing errors on tolerance of individual (Chap. 2), or streams (Chap. 3) of instructions when executing on a single core architecture. Raising further the level of abstraction, procedure-level tolerance (Chap. 4) exposes the effect of dynamic variations to procedure calls for use in software preventive actions. Such exposure leads to a low overhead procedure hopping technique for a tightly coupled processor clusters with 16 cores. This is even more challenging in GP-GPUs and other many-core accelerators where the effect of these variations is not uniformly spread across over thousands processing elements: some are affected more (hence less reliable) than others. In this regard, we propose two methods suitable for GP-GPUs that adaptively predict the delay variations and react accordingly to prevent the timing errors. This first method is an adaptive very long instruction word (VLIW) assignment which is described in Chap. 5. We devise an adaptive compiler method that equalizes the expected lifetime of each processing element by regenerating aging-aware healthy kernels that respond to the specific health state of GP-GPUs. This aging-aware compiler periodically exposes the inherent idleness in VLIW slots and guides its distribution that does matter for the aging. This reallocation mitigates the impacts on lifetime uncertainty and unbalancing among the processing elements. The second method adaptively avoids PVT and aging (PVTA) induced timing errors. Using a model based on supervised learning and PVTA monitoring circuits, we propose hierarchically focused guardbanding (HFG) and demonstrate its effectiveness on GP-GPU architecture at two granularities of observation and adaptation: (i) fine-grained instruction-level; and (ii) coarse-grained kernel-level. Chapter 6 describes HFG in details.

### Chapter 2 Instruction-Level Tolerance

**Abstract** Microprocessors manufactured in nanometer processes are beginning to see variation in timing performance of individual instructions. This chapter considers challenges and opportunities in identifying this variation and methods to combat it for predicting and preventing the timing errors in single-core architectures. We start from instruction-level which is the finest granularity to present the processor functionality. We introduce the notion of instruction-level vulnerability (ILV) to parameterize this variation and use it for architectural and compiler optimizations. To compute ILV, we quantify the effect of voltage and temperature variations on the performance and power of a 32-bit RISC in-order processor in 65 nm TSMC technology at the level of individual instructions. Results show 3.4 ns (68 fanout of 4 or 68FO4) delay variation and  $26.7 \times$  power variation among instructions, and across extreme corners. Our analysis shows that ILV is not uniform across the instruction set. In fact, ILV data partitions instructions into three equivalence classes. Based on this classification, we show how low-overhead monitors and adaptive clocking techniques can be used to enhance performance by a factor of  $1.1 \times -5.5 \times$ .

#### 2.1 Introduction

Designers commonly use conservative guardbands into the operating frequency and voltage to handle these variations to ensure error-free operation within the presence of worse case dynamic variations over circuit lifetime that leads to loss of operational efficiency. An alternative is to use sensor circuits to detect dynamic variations coupled with an adaptive recovery methods for quick on-line error detection and compensation.

Further progress in this area requires a careful analysis of the effect of variations on individual instructions. Here we advance the state of the art through following three means:

1. We analyze the effect of a full range of voltage and temperature variations on the performance and power of the 32-bit in-order RISC LEON-3 [1] processor (Sect. 2.2).

- 2. We introduce the notion of instruction-level vulnerability (ILV) to characterize tolerance of individual instruction to dynamic variations. ILV exposes variation and its effects to the software stack for use in architectural/compiler optimizations. Our results show that ILV is not uniform across the instruction set (Sects. 2.3 and 2.4).

- 3. Using ILV data, we show the effectiveness of a minimally intrusive and cost-effective fine-grained technique to mitigate the dynamic variations that achieves up to 5.5× performance improvement in comparison to the traditional worst-case design.

#### 2.2 Effect of Operating Conditions

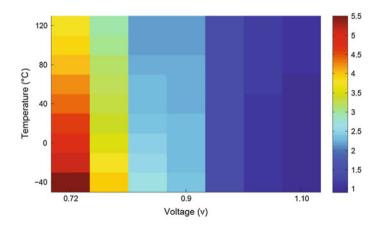

We analyze the effect of operating conditions on the performance and power of the LEON-3 [1] processor compliant with the SPARC V8 architecture. Specifically, we used a temperature range of -40– $125\,^{\circ}$ C, and a voltage range of 0.72– $1.1\,^{\circ}$ V. Figure 2.1 shows how the critical path of the processor varies across corners. The higher voltage results in the shorter critical path, while the lower temperature leads to a higher delay in the low-voltage region (voltage  $\leq 0.9\,^{\circ}$ V), since MOSFET drain current decreases when the temperature is decreased in the deep submicron technologies [2]. These operating condition (hence dynamic) variations cause the critical path delay to increase by a factor of  $6.1\times$  when the operating condition is varied from the one corner to the other. Consequently, a large conservative guardband into the operating frequency is needed to ensure the error-free operation in presence of the dynamic variations.

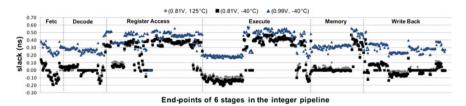

Fig. 2.1 Effect of voltage and temperature variations on the critical path (ns)

#### 2.3 Delay Variation Among Pipeline Stages

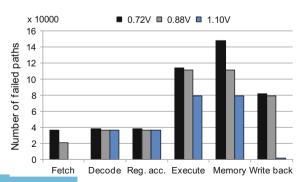

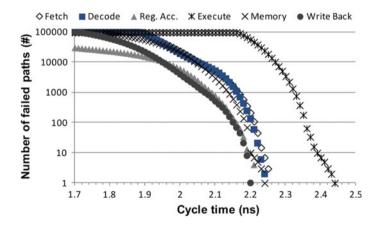

We now evaluate the critical paths of each pipeline stage for a given cycle time, while changing the operating conditions. Figure 2.2 shows the number of failed paths with a negative slack for each parallel pipeline stages across three corners. The cycle time is set at 0.85 ns, and voltage varies from 0.72 to 0.88 V, and then to 1.10 V at a constant temperature of 125 °C. As shown in Fig. 2.2, most of the failed paths lie in the execute and memory stages in all three operating voltages. On the other hand, each of the fetch, decode, and register access stages contains less than 40 K failed paths. Furthermore, there is a relatively small fluctuation in their number of critical paths across voltage variations for these stages. Quantitatively, the memory stage at operating voltage of 0.72 V has  $1.3 \times$ ,  $1.8 \times$ ,  $3.8 \times$  more critical paths in comparison to the execute, write back, and decode stages, respectively. Memory stage at operating voltage of  $1.10 \, \text{V}$  also faces  $1.4 \times$ ,  $1.9 \times$  more critical paths when the voltage drops to 0.88,  $0.72 \, \text{V}$ , respectively.

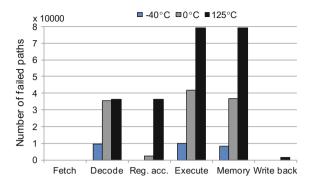

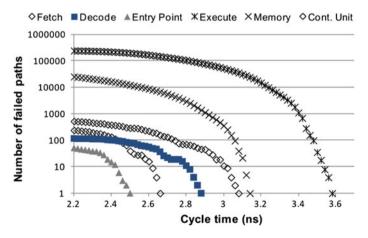

Similarly, in Fig. 2.3 the temperature of processor is varied from –40 to 125 °C at a constant voltage of 1.1 V. As a result, there are no failed paths in the fetch stage when the temperature is varied, and only a small number of failed paths are found in the write back stage at the highest temperature. On the other hand, similar to Fig. 2.2, many paths fail within the execute and memory stages. The execute and memory parts of the processor are not only very sensitive to voltage and temperature variations, but also exhibit a large number of critical paths in comparison to the rest of processor. Therefore, we would anticipate that the instructions that significantly exercise the execute and memory stages are likely to be more vulnerable to voltage and temperature variations.

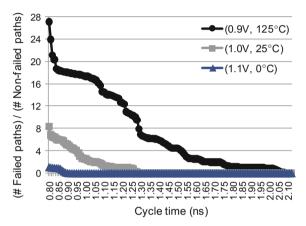

Let us now examine the situation of all paths through the processor under different operating condition and frequency. The Y-axis of Fig. 2.4 shows the proportion of failed paths to nonfailed paths for three corners. We observe that this proportion of failed paths suddenly drops below a certain threshold while the clock is finely scaled with a resolution of  $0.01\,\mathrm{ns}$ . For instance, the proportion falls below 0.5 with only  $0.06\,\mathrm{ns}$  clock scaling at  $(1.10\,\mathrm{V},\,0\,^\circ\mathrm{C})$ ; in the other words, the number of nonfailed paths is twice as many as those which fail. Alternatively, the number of nonfailed

**Fig. 2.2** Effect of voltage variation on the pipeline stages at 125 °C

Fig. 2.3 Effect of temperature variation on the number of failed paths among the pipeline stages at 1.10 V

**Fig. 2.4** The proportion of failed paths to nonfailed paths versus clock

paths is doubled when the cycle time is increased for 0.3 ns at  $(0.9 \text{ V}, 125 \,^{\circ}\text{C})$ . These provide an opportunity for an error-free running of some instructions that will not activate those failed paths.

From the previous analysis, we see that instructions will have different levels of vulnerability to variations depending on the way they exercise the nonuniform critical paths across the various pipeline stages. To capture this phenomenon, we define the concept of instruction-level vulnerability to dynamic variations. The classification of instructions is a valuable mechanism to alleviate the guardbanding and improving performance: (i) within a fixed corner, by acquiring the knowledge about which class of instructions is running, the processor can adapt the guardbanding accordingly, without any need for the intrusive variability sensor/observer; (ii) across every corner, processor can adjust its guardbanding for all class of instructions by using a low-overhead variability observer, e.g., phase locked loop (PLL) [3], and ring oscillators (RO) [4].

### 2.4 Instruction Characterization Methodology and Experimental Results

We use integer pipeline of LEON-3 processor with hardware multiplier/divider units as well as the instruction/data caches to characterize instructions. First, we synthesized the open-source VHDL code of LEON-3 with the TSMC 65 nm technology library (general purpose process) to generate gate-level netlist. The signoff stage for accurate analysis of the operating conditions has been made with Synopsys Prime-Time, using its voltage-temperature scaling features for the composite current source approach of modeling cell behavior. Mentor Graphics' ModelSim is also used for detail gate-level simulations.

#### 2.4.1 Gate-Level Simulation

In the gate-level simulation, for each individual instruction, we apply the Monte Carlo method to observe instruction behavior. To accurately exercise each instruction, we use a normal distribution for the sources, destination, and immediate operands. A large sample of the SPARC ISA is evaluated, including the logical/arithmetic instructions, memory access instructions (load/store), multiply/divide instructions. To quantify the ILV to voltage and temperature variations, we define the **probability of failure** (**PoF**) for each instruction<sub>i</sub> in Eq. 2.1, where  $N_i$  is the total number of clock cycles in Monte Carlo simulation which takes to execute instruction<sub>i</sub> with random operands; and Violation<sub>j</sub> indicates whether there is a violated stage at clock cycle<sub>j</sub> or not.

$$PoFi = \frac{1}{Ni} \sum_{j=1}^{Ni} Violation j$$

$$Violation j = \begin{cases} 1 & \text{If any stage violates at cycle } j \\ 0 & \text{otherwise} \end{cases}$$

(2.1)

In other words,  $PoF_i$  defines as the total number of violated cycles over the total simulated cycles for the instruction<sub>i</sub>. If any of the analyzed stages have one or more violated flip-flop at clock cycle<sub>j</sub>, we consider that stage as a violated stage at cycle<sub>j</sub>. Intuitively, if instruction<sub>i</sub> runs without any violated path,  $PoF_i$  is 0; on the other hand,  $PoF_i$  is 1 if instruction<sub>i</sub> faces at least one violated path in any stage, in every cycle.

| Co    | Corners   |      | (1.1V, -40°C) |      |      | (1.1V, 0°C) |      |      | (1.1V, 125°C) |       |       |       |      |      | (1.0V, 25°C) |       |       |      |  |

|-------|-----------|------|---------------|------|------|-------------|------|------|---------------|-------|-------|-------|------|------|--------------|-------|-------|------|--|

| Cycle | time (ns) | 0.74 | 0.76          | 0.78 | 0.74 | 0.76        | 0.78 | 0.80 | 0.82          | 0.84  | 0.86  | 0.88  | 0.90 | 1.08 | 1.10         | 1.12  | 1.14  | 1.22 |  |

|       | add       | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0            | 0     | 0     | 0    |  |

| etic  | and       | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0            | 0     | 0     | 0    |  |

| 8     | or        | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0            | 0     | 0     | 0    |  |

| 卓     | sll       | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0            | 0     | 0     | 0    |  |

| 8 8   | sra       | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0            | 0     | 0     | 0    |  |

| al &  | srl       | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0            | 0     | 0     | 0    |  |

| .5    | sub       | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0            | 0     | 0     | 0    |  |

| Ĭ     | xnor      | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0            | 0     | 0     | 0    |  |

|       | xor       | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0            | 0     | 0     | 0    |  |

| Mem   | load      | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0.786        | 0     | 0     | 0    |  |

| ž     | store     | 1    | 0             | 0    | 1    | 0           | 0    | 1    | 0             | 0     | 0     | 0     | 0    | 1    | 0.814        | 0     | 0     | 0    |  |

| ul.   | mul       | 1    | 0             | 0    | 1    | 0.967       | 0    | 1    | 0.042         | 0.015 | 0.012 | 0.002 | 0    | 1    | 0.998        | 0.976 | 0.074 | 0    |  |

| &D Wu | div       | 1    | 0.837         | 0    | 1    | 0.948       | 0    | 1    | 0.991         | 0.991 | 0.984 | 0.984 | 0    | 1    | 0.964        | 0.993 | 0.990 | 0    |  |

| ≥≊    | div       | 1    | 0.837         | 0    | 1    | 0.948       | 0    | 1    | 0.991         | 0.991 | 0.984 | 0.984 | 0    | 1    | 0.964        | 0.993 | 0.990 | - 0  |  |

Table 2.1 Probability of failure of ISA at 1.1 and 1.0 V, while varying temperature and frequency

#### 2.4.2 Instruction-Level Delay Variability

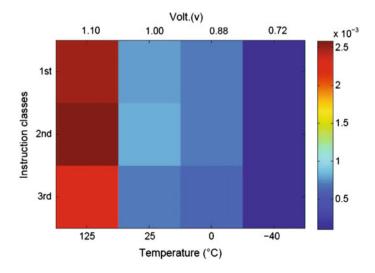

Tables 2.1 and 2.2 summarize the PoF of each evaluated instruction across various corners. We finely change the clock cycle to observe the paths failure for every exercised instruction, and then consequently evaluate its PoF. As shown, instructions exhibit a very wide range of delay under different operating conditions ranges from 0.76 to 4.16 ns. More precisely, the PoF values shown in tables evidence two important facts. First, for their vulnerability to variations, instructions are partitioned into three main classes: (i) the logical/arithmetic instructions, (ii) the memory instructions, and (iii) the multiply/divide instructions. The 1st class shows an abrupt behavior when the clock cycle is slightly varied. Its PoF switches from 1 to 0 with a slight increase in the cycle time (0.02 ns) for every corner, mainly because the path distribution of the exercised part by this class is such that most of the paths have the same length, then we have a all-or-nothing effect, which implies that either all instructions within this class fail or all make it. The 2nd class, the memory instructions, needs much more relaxed cycle time to be able to survive across conditions. For instance, as shown in Table 2.2, only 0.04 ns more guardbanding on the cycle time of the 1st class instruction can guarantee the error-free execution of the memory instructions while they are experiencing 40 °C temperature fluctuation. The 3rd class is the multiply/divide instructions which need higher guardbanding in comparison to the 1st class instruction, ranges from 0.02 ns at (1.1 V, -40 °C) to 0.30 ns at (0.72 V, 125 °C). Since this class highly exercises the execution unit, <sup>1</sup> it has a higher PoF in comparison with the rest of classes in the same clock cycle, for every corner.

Further, based on these results, we can define an adaptive clock cycle for each class of instructions to mitigate the conservative guardbanding, not only within a fixed process corner, but also across corners. All instruction classes act similarly across the wide range of operating conditions: as the cycle time increases gradually, the PoF becomes 0, firstly for the 1st class, then for the 2nd class, and finally for the 3rd

<sup>&</sup>lt;sup>1</sup>Moreover, 64–82% (depends on the corner) of the failed paths in the execution stage lie in the hardware multiplier and divider units.

| Corners     |           | (0.72V, -40°C) |       |       |      | (0.72V, 0°C) |       |       |       |      | (0.72V, 125°C) |       |       |       |       |       |      |

|-------------|-----------|----------------|-------|-------|------|--------------|-------|-------|-------|------|----------------|-------|-------|-------|-------|-------|------|

| Cycle       | time (ns) | 4.10           | 4.12  | 4.14  | 4.16 | 3.58         | 3.60  | 3.62  | 3.64  | 3.66 | 2.88           | 2.90  | 2.92  | 2.94  | 2.98  | 3.00  | 3.20 |

|             | add       | 1              | 0     | 0     | 0    | 1            | 0     | 0     | 0     | 0    | 1              | 0     | 0     | 0     | 0     | 0     | 0    |

| etic        | and       | 1              | 0     | 0     | 0    | 1            | 0     | 0     | 0     | 0    | 1              | 0     | 0     | 0     | 0     | 0     | 0    |

| thm         | or        | 1              | 0     | 0     | 0    | 1            | 0     | 0     | 0     | 0    | 1              | 0     | 0     | 0     | 0     | 0     | 0    |

|             | sll       | 1              | 0     | 0     | 0    | 1            | 0     | 0     | 0     | 0    | 1              | 0     | 0     | 0     | 0     | 0     | 0    |

| & A         | sra       | 1              | 0     | 0     | 0    | 1            | 0     | 0     | 0     | 0    | 1              | 0     | 0     | 0     | 0     | 0     | 0    |

| al &        | srl       | 1              | 0     | 0     | 0    | 1            | 0     | 0     | 0     | 0    | 1              | 0     | 0     | 0     | 0     | 0     | 0    |

| gica        | sub       | 1              | 0     | 0     | 0    | 1            | 0     | 0     | 0     | 0    | 1              | 0     | 0     | 0     | 0     | 0     | 0    |

| Log .       | xnor      | 1              | 0     | 0     | 0    | 1            | 0     | 0     | 0     | 0    | 1              | 0     | 0     | 0     | 0     | 0     | 0    |

|             | xor       | 1              | 0     | 0     | 0    | 1            | 0     | 0     | 0     | 0    | 1              | 0     | 0     | 0     | 0     | 0     | 0    |

| em          | load      | 1              | 0.823 | 0.823 | 0    | 1            | 0.823 | 0.823 | 0     | 0    | 1              | 0.823 | 0.823 | 0.823 | 0.796 | 0.796 | 0    |

| Ň           | store     | 1              | 0.847 | 0.847 | 0    | 1            | 0.847 | 0.847 | 0     | 0    | 1              | 0.847 | 0.847 | 0.847 | 0.823 | 0.823 | 0    |

| ful.<br>Div | mul       | 1              | 0.995 | 0.995 | 0    | 1            | 0.996 | 0.994 | 0     | 0    | 1              | 0.998 | 0.997 | 0.996 | 0.996 | 0.996 | 0    |

| & M         | div       | 1              | 0.995 | 0.995 | 0    | 1            | 0.995 | 0.995 | 0.812 | 0    | 1              | 0.994 | 0.994 | 0.993 | 0.991 | 0.991 | 0    |

**Table 2.2** Probability of failure of ISA at constant voltage 0.72V, while varying temperature and frequency

class. A processor can benefit from this classification by adapting its guardbanding for each class of instruction by acquiring the knowledge about which class of instructions is/will be running.

#### 2.4.3 Less Intrusive Variation-Tolerant Technique

All intrusive techniques [5–7] try to avoid timing failure for instructions that activate the critical paths by dynamically switching to two-cycle operation. These expensive, instruction by instruction timing adjustment techniques do not expose opportunity for further software-level optimizations especially for sequences and classes of instructions. Therefore, we could have an advanced dynamic clock speed adaptation technique, possibly compiler driven, which can quickly decide on the clock speed of the processor at a very fine-grained [8], just looking at the fetched instructions and keeping track of their entry into the stages, and at the same time monitoring the current corner with a low-overhead monitoring hardware [3, 4]. This technique not only provides great performance enhancement for processor, but also is a step forward toward a less intrusive circuit monitoring and cost-effective robust design.

Table 2.3 shows how a program consisting of various classes of instructions can benefit by this technique under different operating conditions: the performance improvement when processor runs a program only consists of specific classes, in comparison to the traditional worst-case design. For instance, at the typical operating condition (1.0 V, 25 °C) processor can decrease the cycle time form 4.16 ns (Table 2.2) to 1.22 ns (Table 2.1), and consequently achieves  $3.4\times$  speed improvement, when its running program consists of all three classes. It can further reduce the cycle time to  $1.12\,\text{ns}$  (3.7× speedup) when only the 1st, and 2nd classes of instructions are used in its program. As shown, the proposed solution can greatly achieve  $1.1\times-5.5\times$  performance improvement depends on the type of instruction and the operating condition.

| Vol. (V) | Temp. (°C) | 1st and 2nd class | 1st, 2nd, 3rd class |

|----------|------------|-------------------|---------------------|

| 1.10     | -40        | 5.5×              | 5.3×                |

| 1.10     | 0          | 5.5×              | 5.3×                |

| 1.10     | 125        | 5.1×              | 4.6×                |

| 1.00     | 25         | 3.7×              | 3.4×                |

| 0.88     | -40        | 3.9×              | 3.7×                |

| 0.88     | 0          | 3.9×              | 3.7×                |

| 0.88     | 125        | 3.9×              | 3.5×                |

| 0.72     | 0          | 1.1×              | 1.1×                |

| 0.72     | 125        | 1.3×              | 1.3×                |

**Table 2.3** Performance improvement for different classes of instructions

#### 2.4.4 Power Variability

From delay variability of instructions, we examine now variation of power consumption across and within process corners. The total power consumption of the instruction classes under four operating conditions is shown in Fig. 2.5, when the cycle time is adjusted for each class accordingly, i.e., the best frequency for each class is applied. As a result, all three classes of instructions experience a wide range of total power variability  $(0.1-2.6\,\mathrm{mW})$ ,  $1.15\times$  intra-corner power variation (across the three classes) due to exercising various parts of processor, and  $26.7\times$  inter-corner power variation, at maximum. This implies that ILV could potentially expose opportunity for further software-level optimizations for both performance and power.

Fig. 2.5 Intera- and inter-corner total power (W) variability of the instruction classes

#### 2.5 Chapter Summary

The concept of instruction-level vulnerability to dynamic voltage and temperature variations is defined. Based on that, all exercised instructions in the integer pipeline of LEON-3 are partitioned into three classes for the full range of operating condition: (i) the logical and arithmetic instructions, (ii) the memory instructions, and (iii) the multiply and divide instructions. Using this classification in conjunction with less intrusive variability observers provides architectural/compiler optimizations a great opportunity to enhance processor performance by  $1.1 \times -5.5 \times$ , in TSMC 65 nm technology. It is also a step forward toward a low-overhead, efficient, and cost-effective robust design.

#### References

- 1. Leon3. http://www.gaisler.com/cms/

- R. Kumar, V. Kursun, Reversed temperature-dependent propagation delay characteristics in nanometer cmos circuits. IEEE Trans. Circuits Syst. II Express Briefs 53(10), 1078–1082 (2006)

- K. Kang, S.P. Park, K. Kim, K. Roy, On-chip variability sensor using phase-locked loop for detecting and correcting parametric timing failures. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 18(2), 270–280 (2010)

- M. Bhushan, A. Gattiker, M.B. Ketchen, K.K. Das, Ring oscillators for CMOS process tuning and variability control. IEEE Trans. Semicond. Manufact. 19(1), 10–18 (2006)

- 5. D. Ernst, S. Das, S. Lee, D. Blaauw, T. Austin, T. Mudge, N.S. Kim, K. Flautner, Razor: circuit-level correction of timing errors for low-power operation. Micro, IEEE, **24**(6), 10–20 (2004)

- K.A. Bowman, J.W. Tschanz, S.L. Lu, P.A. Aseron, M.M. Khellah, A. Raychowdhury, B.M. Geuskens, C. Tokunaga, C.B. Wilkerson, T. Karnik, V.K. De, A 45 nm resilient microprocessor core for dynamic variation tolerance. IEEE J. Solid-State Circuits 46(1), 194–208 (2011)

- D. Bull, S. Das, K. Shivshankar, G. Dasika, K. Flautner, D. Blaauw, A power-efficient 32b ARM ISA processor using timing-error detection and correction for transient-error tolerance and adaptation to PVT variation, in 2010 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) (2010), pp. 284–285

- 8. J. Tschanz, N.S. Kim, S. Dighe, J. Howard, G. Ruhl, S. Vangal, S. Narendra, Y. Hoskote, H. Wilson, C. Lam, M. Shuman, C. Tokunaga, D. Somasekhar, S. Tang, D. Finan, T. Karnik, N. Borkar, N. Kurd, V. De, Adaptive frequency and biasing techniques for tolerance to dynamic temperature-voltage variations and aging. In *IEEE International Solid-State Circuits Conference*, 2007. ISSCC 2007. Digest of Technical Papers (2007), pp. 292–604

## **Chapter 3 Sequence-Level Tolerance**

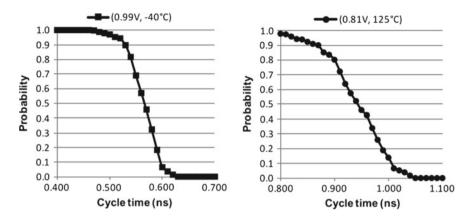

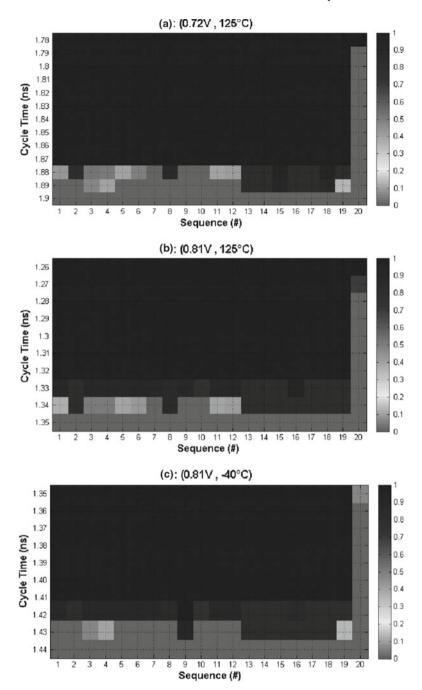

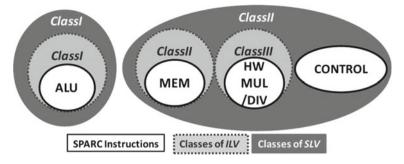

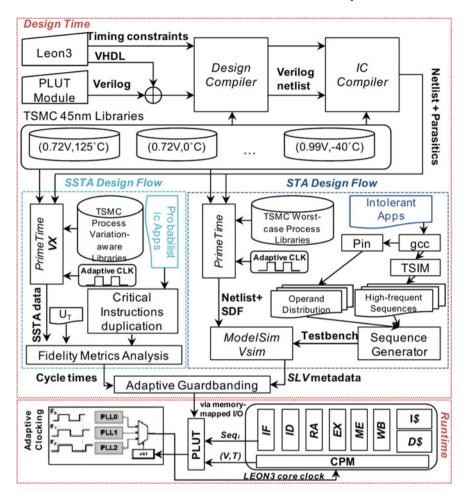

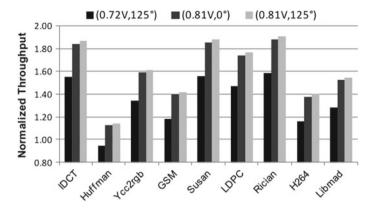

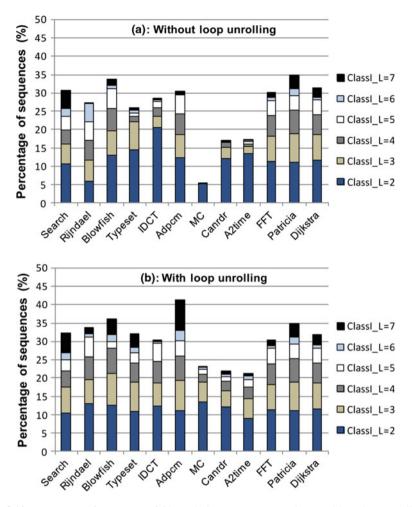

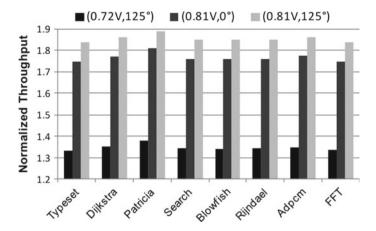

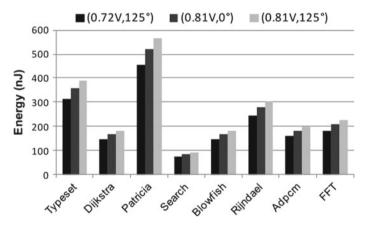

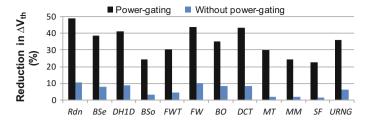

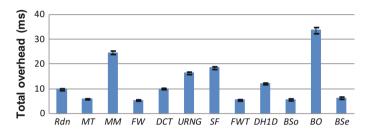

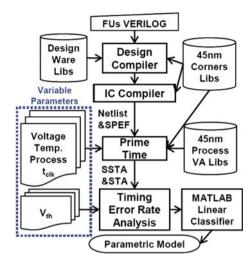

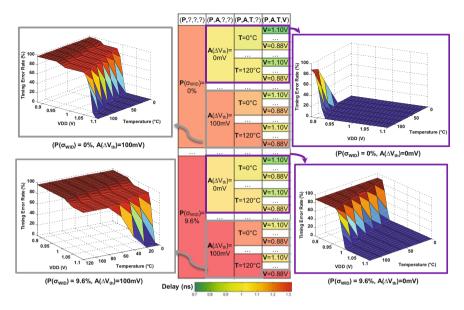

**Abstract** This chapter presents a method for predicting and preventing the timing errors for a sequence of instruction in single-core architectures. We introduce the notion of sequence-level vulnerability (SLV) that utilizes circuit-level vulnerability for constructing high-level software knowledge as metadata. In effect, the SLV metadata partitions sequences of integer SPARC instructions into two equivalence classes to enable an adaptive guardbanding technique to adapt the clock frequency simultaneously for dynamic voltage and temperature variations, as well as adapting to the different classes of the instruction sequences. The proposed technique achieves on an average 1.6× speedup for error-intolerant applications compared to recent work (Hoang, Exploring circuit timing-aware language and compilation, 2011, [1]). However, in reality, applications exhibit varying degrees of tolerance to error in computations. This chapter also proposes an adaptive guardbanding technique for errortolerant (probabilistic) applications where application execution does not assume an error-free execution hardware. The proposed technique leverages a combination of accurate design time analysis and a minimally intrusive runtime technique to mitigate process, voltage, and temperature (PVT) variations for a near-zero area overhead. We demonstrate our approach on a 32-bit in-order RISC processor with full post placement and routing (P&R) layout results in TSMC 45 nm technology. The adaptive guardbanding technique eliminates traditional guardbands on clock frequency using information from PVT variations and application-specific requirements on computational accuracy. For probabilistic applications, the adaptive technique guarantees the error-free operation of a set of paths of the processor that always require correct timing (vulnerable paths) while reducing the cost of guardbanding for the rest of the paths (invulnerable paths). This increases the throughput of probabilistic applications upto 1.9× over the traditional worst-case design. The proposed technique has 0.022% area overhead, and imposes only 0.034 and 0.031% total power overhead for intolerant and probabilistic applications respectively.

#### 3.1 Introduction

Several recent efforts have focused on measures to mitigate variability through innovations in circuit-level designs. These methods strive to achieve instruction

executions *exactly* as specified by the application programs. In contrast, **probabilistic** programs can exhibit enhanced error resilience at the application-level when multiple valid output values are permitted. Accurate design time analysis coupled with efficient runtime techniques are required to overcome the variability challenges. We propose a near-zero area overhead adaptive guardbanding technique to meet application-specific requirements on computational accuracy. This chapter makes the following contributions:

- 1. We present a method to relate low-level hardware vulnerability information obtained using accurate and practical variation-aware analysis to high-level knowledge in software. Our analysis flow considers the dynamic voltage and temperature as well as static process variations, and validates results on a full post P&R layout of a 32-bit in-order RISC processor.

- 2. We propose an adaptive guardbanding technique to dynamically adjust the cycle time to PVT variations and application-level computation accuracy. For probabilistic applications represented by multimedia benchmarks from MiBench [2] and MediaBench [3], the technique achieves up to 1.9× throughput improvement in comparison to the traditional worst-case design.

- 3. For error-intolerant applications, we introduce the notion of sequence-level vulnerability (SLV) to dynamic voltage and temperature variations. Our experimental results and analysis show that SLV is not uniform across sequences obtained from a large set of general purpose benchmarks [2–6]. Effectively, the SLV partitions sequences of integer SPARC instructions into two classes: ClassI, which only consists of the arithmetic/logical instructions; and ClassII, a mixture of all types of instructions. We also show the effectiveness of compiler technique to achieve a favorable mix of sequences. Using SLV enables the processor to achieve 1.6× average speedup for intolerant applications, compared to [1], by adapting the cycle time for dynamic variations and different instruction sequences. The minimally intrusive and cost-effective guardbanding in software greatly reduces the hardware cost with respect to the above-mentioned circuit techniques. Full layout results on TSMC 45 nm technology show that the proposed guardbanding imposes only 0.031 and 0.034% total power overhead for the probabilistic and the intolerant applications respectively. The total area overhead is 0.022%.

#### 3.2 PVT Variations

In this section, we analyze the delay variations caused by PVT variations on the paths of the 32-bit in-order LEON3 processor compliant with the SPARC V8 architecture. This choice is keeping in view of the recent trends toward array processor architectures containing many simple RISC cores, e.g., GPUs [7], TILERA [8], and Platform 2012 [9, 10]. More importantly, the availability of an advanced open-source RISC core with full back-end details is critical to accurate variation analysis. We note that other efforts for complex high-performance cores such as IBM POWER6 also con-

3.2 PVT Variations 23

Fig. 3.1 Nonuniform slack variation of the integer pipeline stages caused by PVT with cycle time at 0.83 ns

firm that vulnerability is not uniform across the instructions set [11]. While different instruction sets will lead to different grouping of instructions depending upon the processor architecture and implementation, our methodology can be applied as long as there is a nonuniform vulnerability across the instructions.

Specifically, the effects of a full range of dynamic variations (an industrial temperature range of -40-125 °C, and a voltage range of 0.72-0.99 V) as well as static process parameters variations (die-to-die and within-die) are analyzed on all paths throughout the entire integer pipeline of LEON3. Figure 3.1 illustrates the delay variation in the six stages of the pipeline that results in positive/negative slacks for the flip-flops connected to the endpoints of the paths. The cycle time is set at 0.83 ns to meet the timing requirement of the typical-corner (0.9 V, 25 °C, TT). A higher voltage of 0.99 V results in shorter delay (positive slack), while the lower temperature leads to a higher delay in the low-voltage region below 0.9 V, since MOSFET drain current decreases when the temperature is decreased in nanometer CMOS technologies [12]. In addition to these dynamic operating conditions, the static process variations exacerbate the delay variation across various pipeline stages; Sect. 3.2.2 describes the details of modeling the process variations. Given such variations across operating conditions and across different parts of the design, an adaptive guardbanding of the operating frequency is useful to ensure the error-free operation. Such a guardband can be much less conservative than a statically determined guardband. We divide pipeline paths into two groups: (a) Vulnerable Paths (VP): A set of paths that always require correct timing and any delay variability may result in catastrophic architectural failures and consequently visible errors in the outputs of a program; and (b) Invulnerable Paths (IP): A set of paths that do not require 100% timing correctness. The delay variation in IP does not cause catastrophic architectural failures since it affects only the vector of elastic outputs. The vector of elastic outputs does not require the complete numerical correctness. Thus, the delay variation in IP may degrade of the quality of fidelity metrics of the probabilistic applications. Specifically for LEON3 pipeline shown in Fig. 3.1, a 20% voltage variation results in many negative slack values at the endpoints of the fetch and decode stages which causes the wrong instructions to be executed. Thus, the paths that lie in these stages are considered as VP and must always meet the setup time of flip-flops in PVT variation. On the other hand, the scenario for IP is different. For example in the execution stage, some endpoints do not suffer from delay variation at all (those paths with a positive

slack), and some endpoints have negative slack when voltage variation occurs. The execution stage has much more flexibility to deal with delay variation as long as it can produce an acceptable fidelity metric.

In Sect. 3.3.1, we present guardbanding technique that seeks to guardband VP for error-free operation, and at the same time effectively reduces the cost of guardbands on IP against fidelity metric of programs that are tolerant to imprecise and approximate computations. The tolerance levels can be specified based on algorithmic classifications such as RMS [13]. Section 3.4 also covers another adaptive guardbanding technique for intolerant applications in the general case.

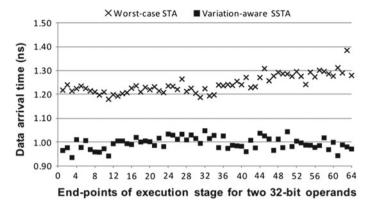

#### 3.2.1 Conventional Static Timing Analysis

Conventional static timing analysis (STA) calculates the maximum delay variation using the worst-case corner, by simply combining the absolute worst-case combination of the process, voltage, and temperature parameters. The cycle time is finely varied to observe the behavior of the pipeline stages. The number of failed paths (i.e., paths with negative slack) for each stage using the STA in the worst-corner (0.72 V, 0 °C, Slow NMOS-Slow PMOS) is shown in Fig. 3.2. Increasing the cycle time from 1.8 to 2.25 ns reduces the number of failed path from hundreds of thousand paths to zero path for all stages except the execution stage which has a higher delay. The execution stage needs 10% more guardbanding, i.e., the clock cycle of 2.5 ns. Further, our earlier analysis [14] shows that the execution and memory stages are highly vulnerable to dynamic variations. By setting the cycle time at 2.25 ns, we guarantee that no path will fail within the fetch, decode, register access, memory, and write back stages even in the worst-case process parameter variation. The paths in these stages are considered as VP because: (i) any failure in fetch or decode stages

Fig. 3.2 Number of failed paths of LEON3 pipeline using STA

3.2 PVT Variations 25

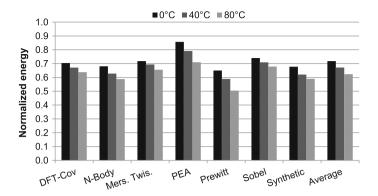

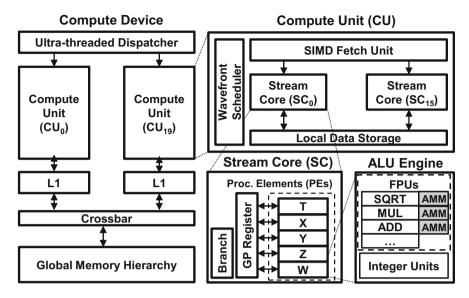

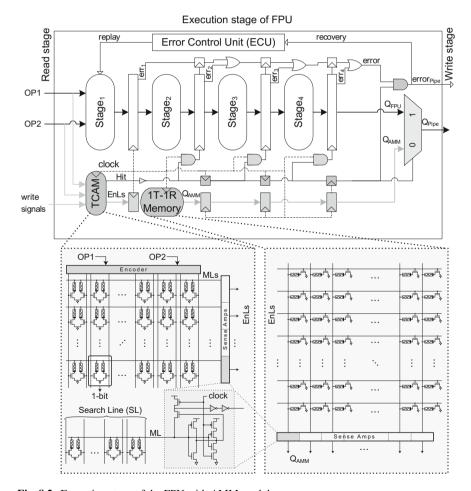

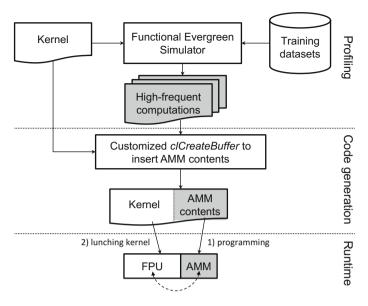

may cause the wrong instructions to be executed that cannot be masked even within the probabilistic application; and (ii) any failure in the register/memory/write back stages may cause an illegal access/operation on the memory/registers. It is therefore not surprising that both Intel resilient processor [15] and relaxed-reliability cores in ERSA [16] consider sufficient guardbanding in register stage, memory management unit, and L1 instruction cache. By sufficient guardbanding on VP through STA, the error-free operation of VP is guaranteed even if these paths display the worst-case process characteristics.